## Si4030/31/32-B1

## Si4030/31/32 ISM TRANSMITTER

#### **Features**

- Frequency range

- 240–930 MHz (Si4031/32)

- 900–960 MHz (Si4030)

- Output Power Range

- +1 to +20 dBm (Si4032)

- -8 to +13 dBm (Si4030/31)

- Low Power Consumption

- Si4032

- 85 mA @ +20 dBm

- Si4030/31

- 30 mA @ +13 dBm

- Data Rate = 0.123 to 256 kbps

- FSK, GFSK, and OOK modulation

- Power Supply = 1.8 to 3.6 V

- Ultra low power shutdown mode

- Wake-up timer

- Integrated 32 kHz RC or 32 kHz XTAI

- Integrated voltage regulators

- Configurable packet handler

- TX 64 byte FIFO

- Low battery detector

- Temperature sensor and 8-bit ADC

- -40 to +85 °C temperature range

- Integrated voltage regulators

- Frequency hopping capability

- On-chip crystal tuning

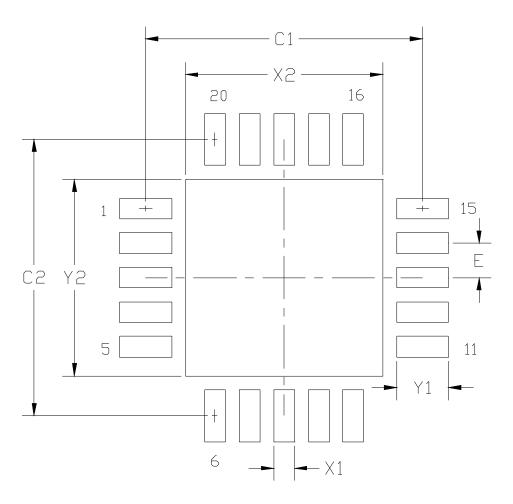

- 20-Pin QFN package

- Low BOM

- Power-on-reset (POR)

## **Applications**

- Remote control

- Home security & alarm

- Telemetry

- Personal data logging

- Toy control

- Wireless PC peripherals

- Remote meter reading

- Remote keyless entry

- Home automation

- Industrial control

- Sensor networks

- Health monitors

## Description

Silicon Laboratories' Si4030/31/32 devices are highly integrated, single-chip wireless ISM transmitters. The high-performance EZRadioPRO $^{\otimes}$  family includes a complete line of transmitters, receivers, and transceivers allowing the RF system designer to choose the optimal wireless part for their application.

The Si4030/31/32 offers advanced radio features including continuous frequency coverage from 240–960 MHz with adjustable power output levels of –8 to +13 dBm on the Si4030/31 and +1 to +20 dBm on the Si4032. Power adjustments are made in 3 dB steps. The Si4030/31/32's high level of integration offers reduced BOM cost while simplifying the overall system design. The Si4032's Industry leading +20 dBm output power ensures extended range and improved link performance.

Additional system features such as an automatic wake-up timer, low battery detector, 64 byte TX FIFO, and automatic packet handling reduce overall current consumption and allow the use of lower-cost system MCUs. An integrated temperature sensor, general purpose ADC, power-on-reset (POR), and GPIOs further reduce overall system cost and size.

The direct digital transmit modulation and automatic PA power ramping ensure precise transmit modulation and reduced spectral spreading ensuring compliance with global regulations including FCC, ETSI, and ARIB regulations.

An easy-to-use calculator is provided to quickly configure the radio settings, simplifying customer's system design and reducing time to market.

Ordering Information: See page 53.

Patents pending

## **Functional Block Diagram**

#### Si4030/31/32 nIRQ nSEL SDN **DIGLDO VDR LPLDO VDD** 30M XTAL Digital Logic OSC RF LDO $\bigcirc$ PA RAMP Controller & - SCLK Register Bank PWR CTRL PLL LDO -SDO \_ SCK **VCO LDO** TX DATA FIFO - SDI SPI Packet Handler VCO PA 30MHz & TX Interface **LPF** Wake-Up Timer PA\_RAMP PWR\_CTRL Delta Sigma ÷Ν Modulator RC 32K OSC 32K XTAL POR (2) (2) GPIO\_0 GPIO\_1 GPIO\_2 General **Battery Level** Temperature Purpose 8Bit Detector Sensor ADC

# TABLE OF CONTENTS

| <u>Section</u>                                    | <u>Page</u> |

|---------------------------------------------------|-------------|

| 1. Electrical Specifications                      |             |

| 1.1. Definition of Test Conditions                |             |

| 2. Functional Description                         |             |

| 2.1. Operating Modes                              |             |

| 3. Controller Interface                           |             |

| 3.1. Serial Peripheral Interface (SPI)            |             |

| 3.2. Operating Mode Control                       |             |

| 3.3. Interrupts                                   |             |

| 3.4. System Timing                                |             |

| 3.5. Frequency Control                            |             |

| 4. Modulation Options                             |             |

| 4.1. Modulation Type                              |             |

| 4.2. Modulation Data Source                       |             |

| 5. Internal Functional Blocks                     |             |

| 5.1. Synthesizer                                  |             |

| 5.2. Power Amplifier                              |             |

| 5.3. Crystal Oscillator                           |             |

| 5.4. Regulators                                   |             |

| 6. Data Handling and Packet Handler               |             |

| 6.1. TX FIFO                                      |             |

| 6.2. Packet Configuration                         |             |

| 6.3. Packet Handler TX Mode                       |             |

| 6.4. Data Whitening, Manchester Encoding, and CRC |             |

| 6.5. Synchronization Word Configuration           |             |

| 6.6. TX Retransmission and Auto TX                |             |

| 7. Auxiliary Functions                            |             |

| 7.1. Smart Reset                                  |             |

| 7.2. Microcontroller Clock                        | 40          |

| 7.3. General Purpose ADC                          | 41          |

| 7.4. Temperature Sensor                           | 42          |

| 7.5. Low Battery Detector                         | 44          |

| 7.6. Wake-Up Timer                                |             |

| 7.7. GPIO Configuration                           |             |

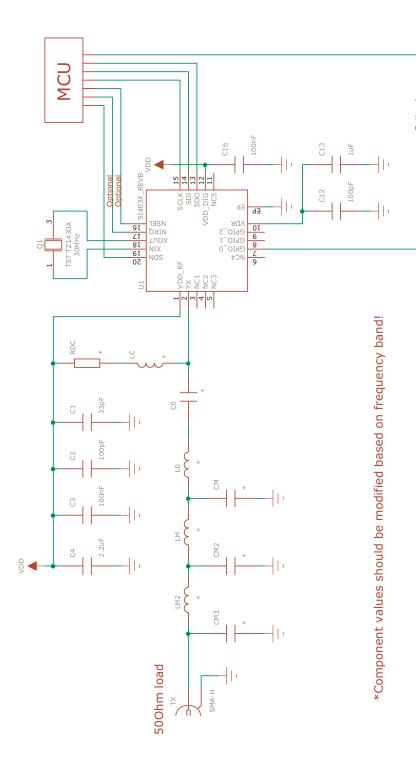

| 8. Reference Design                               |             |

| 9. Application Notes and Reference Designs        |             |

| 10. Customer Support                              |             |

| 11. Register Table and Descriptions               |             |

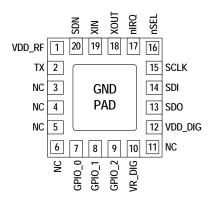

| 12. Pin Descriptions: Si4030/31/32                |             |

| 13. Ordering Information                          |             |

# Si4030/31/32-B1

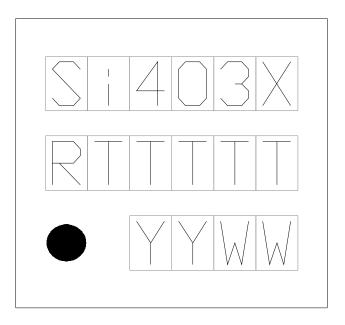

| 14. Package Markings (Top Marks)   | 53 |

|------------------------------------|----|

| 14.1. Si4030/31/32 Top Mark        |    |

| 14.2. Top Mark Explanation         |    |

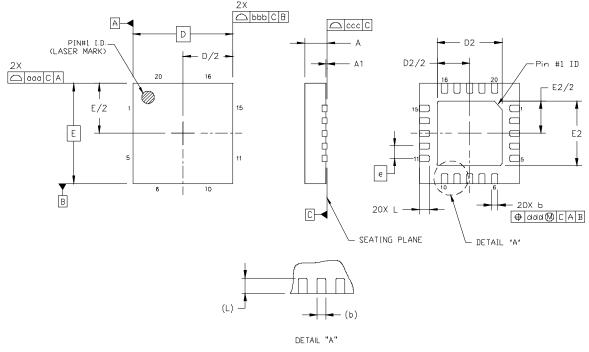

| 15. Package Outline: Si4030/31/32  |    |

| 16. PCB Land Pattern: Si4030/31/32 |    |

| Document Change List               |    |

| Contact Information                |    |

# LIST OF FIGURES

| Figure 1. SPI Timing                                                 | 15 |

|----------------------------------------------------------------------|----|

| Figure 2. SPI Timing—READ Mode                                       | 16 |

| Figure 3. SPI Timing—Burst Write Mode                                |    |

| Figure 4. SPI Timing—Burst Read Mode                                 | 16 |

| Figure 5. State Machine Diagram                                      | 17 |

| Figure 6. TX Timing                                                  |    |

| Figure 7. Frequency Deviation                                        | 25 |

| Figure 8. FSK vs. GFSK Spectrums                                     | 27 |

| Figure 9. Microcontroller Connections                                | 30 |

| Figure 10. PLL Synthesizer Block Diagram                             | 31 |

| Figure 11. FIFO Threshold                                            | 34 |

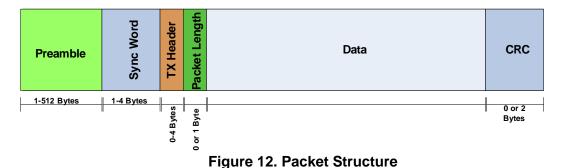

| Figure 12. Packet Structure                                          | 35 |

| Figure 13. Multiple Packets in TX Packet Handler                     | 36 |

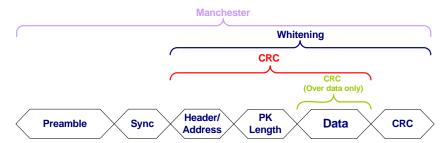

| Figure 14. Operation of Data Whitening, Manchester Encoding, and CRC | 37 |

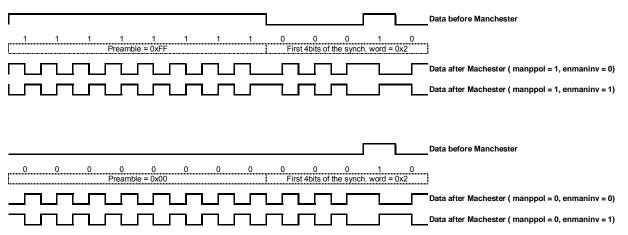

| Figure 15. Manchester Coding Example                                 | 37 |

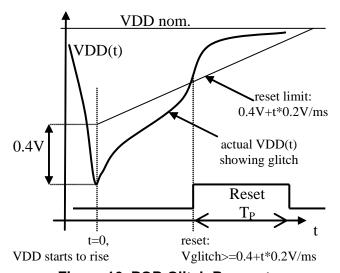

| Figure 16. POR Glitch Parameters                                     | 39 |

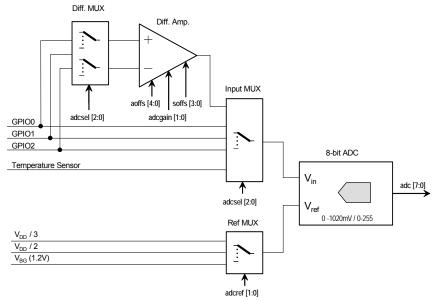

| Figure 17. General Purpose ADC Architecture                          | 41 |

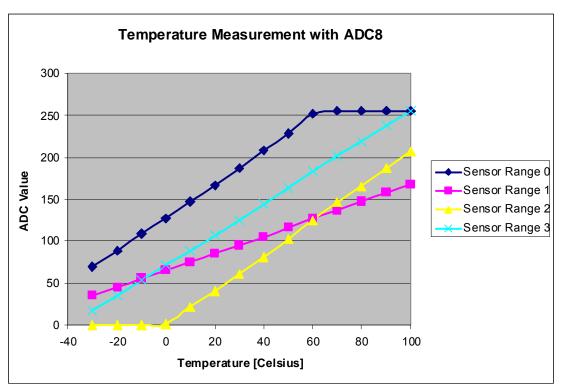

| Figure 18. Temperature Ranges using ADC8                             | 43 |

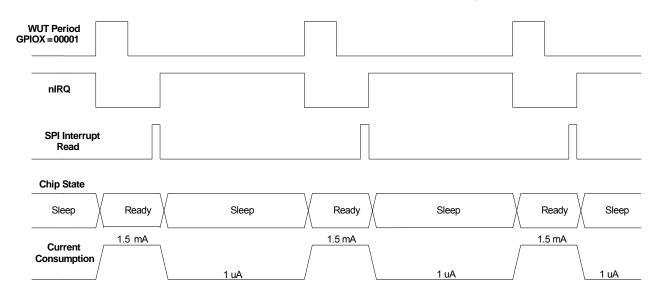

| Figure 19. WUT Interrupt and WUT Operation                           | 46 |

| Figure 20. Si4031 Reference Design Schematic                         | 48 |

| Figure 21. 20-Pin Quad Flat No-Lead (QFN)                            | 54 |

| Figure 22. PCB Land Pattern                                          | 55 |

# LIST OF TABLES

| Table 1. DC Characteristics <sup>1</sup>                            | 7  |

|---------------------------------------------------------------------|----|

| Table 2. Synthesizer AC Electrical Characteristics <sup>1</sup>     |    |

| Table 3. Transmitter AC Electrical Characteristics <sup>1</sup>     |    |

| Table 4. Auxiliary Block Specifications <sup>1</sup>                | 10 |

| Table 5. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and nIRQ) |    |

| Table 6. GPIO Specifications (GPIO 0, GPIO 1, and GPIO 2)           |    |

| Table 7. Absolute Maximum Ratings                                   | 12 |

| Table 8. Operating Modes                                            | 14 |

| Table 9. Serial Interface Timing Parameters                         | 15 |

| Table 10. Operating Modes Response Time                             | 17 |

| Table 11. Frequency Band Selection                                  | 23 |

| Table 12. Packet Handler Registers                                  | 36 |

| Table 13. POR Parameters                                            | 39 |

| Table 14. Temperature Sensor Range                                  |    |

| Table 15. Register Descriptions                                     | 50 |

| Table 16. Package Dimensions                                        | 54 |

| Table 17. PCB Land Pattern Dimensions                               | 56 |

## 1. Electrical Specifications

Table 1. DC Characteristics<sup>1</sup>

| Parameter                     | Symbol                  | Conditions                                                                                                                      | Min | Тур | Max | Units |

|-------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply Voltage Range          | $V_{DD}$                |                                                                                                                                 | 1.8 | 3.0 | 3.6 | V     |

| Power Saving Modes            | I <sub>Shutdown</sub>   | RC Oscillator, Main Digital Regulator, and Low Power Digital Regulator OFF <sup>2</sup>                                         | _   | 15  | 50  | nA    |

|                               | I <sub>Standby</sub>    | Low Power Digital Regulator ON (Register values retained) and Main Digital Regulator, and RC Oscillator OFF                     | _   | 450 | 800 | nA    |

|                               | I <sub>Sleep</sub>      | RC Oscillator and Low Power Digital Regulator ON (Register values retained) and Main Digital Regulator OFF                      | _   | 1   | _   | μΑ    |

|                               | I <sub>Sensor-LBD</sub> | Main Digital Regulator and Low Battery Detector ON,<br>Crystal Oscillator and all other blocks OFF <sup>2</sup>                 | _   | 1   | _   | μΑ    |

|                               | I <sub>Sensor-TS</sub>  | Main Digital Regulator and Temperature Sensor ON,<br>Crystal Oscillator and all other blocks OFF <sup>2</sup>                   | _   | 1   | _   | μΑ    |

| I <sub>Re</sub>               |                         | Crystal Oscillator and Main Digital Regulator ON, all other blocks OFF. Crystal Oscillator buffer disabled                      | _   | 800 | _   | μA    |

| TUNE Mode Current             | I <sub>Tune</sub>       | Synthesizer and regulators enabled                                                                                              | _   | 8.5 | _   | mA    |

| TX Mode Current<br>—Si4032    | I <sub>TX_+20</sub>     | txpow[2:0] = 111 (+20 dBm) Using Silicon Labs' Reference Design. TX current consumption is dependent on match and board layout. | _   | 85  | _   | mA    |

| TX Mode Current<br>—Si4030/31 | I <sub>TX_+13</sub>     | txpow[2:0] = 111 (+13 dBm) Using Silicon Labs' Reference Design. TX current consumption is dependent on match and board layout. | _   | 30  | _   | mA    |

|                               | I <sub>TX_+1</sub>      | txpow[2:0] = 011 (+1 dBm) Using Silicon Labs' Reference Design. TX current consumption is dependent on match and board layout.  | _   | 18  | _   | mA    |

- 1. All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

- **2.** Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

Table 2. Synthesizer AC Electrical Characteristics<sup>1</sup>

| Parameter                                       | Symbol              | Conditions                                                                                                                | Min | Тур    | Max | Units              |

|-------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|--------------------|

| Synthesizer Frequency<br>Range—Si4031/32        | F <sub>SYN</sub>    |                                                                                                                           | 240 | _      | 930 | MHz                |

| Synthesizer Frequency<br>Range—Si4030           | F <sub>SYN</sub>    |                                                                                                                           | 900 | _      | 960 | MHz                |

| Synthesizer Frequency                           | F <sub>RES-LB</sub> | Low Band, 240–480 MHz                                                                                                     | _   | 156.25 | -   | Hz                 |

| Resolution <sup>2</sup>                         | F <sub>RES-HB</sub> | High Band, 480–960 MHz                                                                                                    | _   | 312.5  | _   | Hz                 |

| Reference Frequency<br>Input Level <sup>2</sup> | f <sub>REF_LV</sub> | When using external reference signal driving XOUT pin, instead of using crystal. Measured peak-to-peak (V <sub>PP</sub> ) | 0.7 | _      | 1.6 | V                  |

| Synthesizer Settling Time <sup>2</sup>          | t <sub>LOCK</sub>   | Measured from exiting Ready mode with XOSC running to any frequency. Including VCO calibration.                           | _   | 200    | _   | μs                 |

| Residual FM <sup>2</sup>                        | $\Delta F_{RMS}$    | Integrated over ±250 kHz bandwidth (500 Hz lower bound of integration)                                                    | _   | 2      | 4   | kHz <sub>RMS</sub> |

| Phase Noise <sup>2</sup>                        | Lφ(f <sub>M</sub> ) | ΔF = 10 kHz                                                                                                               | _   | -80    | _   | dBc/Hz             |

|                                                 |                     | ΔF = 100 kHz                                                                                                              | _   | -90    | _   | dBc/Hz             |

|                                                 |                     | ΔF = 1 MHz                                                                                                                | _   | -115   | _   | dBc/Hz             |

|                                                 |                     | ΔF = 10 MHz                                                                                                               | _   | -130   | _   | dBc/Hz             |

- **1.** All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

- **2.** Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

Table 3. Transmitter AC Electrical Characteristics<sup>1</sup>

| Parameter                                                    | Symbol                | Conditions                                                                             | Min    | Тур   | Max  | Units |

|--------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------|--------|-------|------|-------|

| TX Frequency<br>Range—Si4031/32                              | F <sub>TX</sub>       |                                                                                        | 240    | _     | 930  | MHz   |

| TX Frequency<br>Range—Si4030                                 | F <sub>TX</sub>       |                                                                                        | 900    | _     | 960  | MHz   |

| FSK Data Rate <sup>2</sup>                                   | DR <sub>FSK</sub>     |                                                                                        | 0.123  | _     | 256  | kbps  |

| OOK Data Rate <sup>2</sup>                                   | DR <sub>OOK</sub>     |                                                                                        | 0.123  | _     | 40   | kbps  |

| Modulation Deviation                                         | Δf1                   | 860–960 MHz                                                                            | ±0.625 |       | ±320 | kHz   |

|                                                              | Δf2                   | 240-860 MHz                                                                            | ±0.625 |       | ±160 | kHz   |

| Modulation Deviation<br>Resolution <sup>2</sup>              | $\Delta f_{RES}$      |                                                                                        | _      | 0.625 | _    | kHz   |

| Output Power<br>Range —Si4032 <sup>3</sup>                   | P <sub>TX</sub>       |                                                                                        | +1     | _     | +20  | dBm   |

| Output Power<br>Range—Si4030/31 <sup>3</sup>                 | P <sub>TX</sub>       |                                                                                        | -8     | _     | +13  | dBm   |

| TX RF Output Steps <sup>2</sup>                              | ΔP <sub>RF_OUT</sub>  | controlled by txpow[2:0]                                                               | _      | 3     |      | dB    |

| TX RF Output Level <sup>2</sup><br>Variation vs. Temperature | ΔP <sub>RF_TEMP</sub> | −40 to +85 °C                                                                          | _      | 2     |      | dB    |

| TX RF Output Level<br>Variation vs. Frequency <sup>2</sup>   | ΔP <sub>RF_FREQ</sub> | Measured across any one frequency band                                                 | _      | 1     | _    | dB    |

| Transmit Modulation<br>Filtering <sup>2</sup>                | B*T                   | Gaussian Filtering Bandwith Time<br>Product                                            | _      | 0.5   | _    |       |

| Spurious Emissions <sup>2</sup>                              | P <sub>OB-TX1</sub>   | P <sub>OUT</sub> = 13 dBm,<br>Frequencies <1 GHz                                       | _      | _     | -54  | dBm   |

|                                                              | P <sub>OB-TX2</sub>   | 1–12.75 GHz, excluding harmonics                                                       | _      | _     | -54  | dBm   |

| Harmonics <sup>2</sup>                                       | P <sub>2HARM</sub>    | Using reference design TX matching                                                     | _      | _     | -42  | dBm   |

|                                                              | P <sub>3HARM</sub>    | network and filter with max output power. Harmonics reduce linearly with output power. | _      | _     | -42  | dBm   |

- **1.** All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

- **2.** Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

- 3. Output power is dependent on matching components and board layout.

Table 4. Auxiliary Block Specifications<sup>1</sup>

| Parameter                                                            | Symbol               | Conditions                                                                                                | Min     | Тур  | Max | Units  |

|----------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|---------|------|-----|--------|

| Temperature Sensor<br>Accuracy <sup>2</sup>                          | TS <sub>A</sub>      | After calibrated via sensor offset register tvoffs[7:0]                                                   | _       | 0.5  | _   | °C     |

| Temperature Sensor<br>Sensitivity <sup>2</sup>                       | TS <sub>S</sub>      |                                                                                                           | _       | 5    | _   | mV/°C  |

| Low Battery Detector<br>Resolution <sup>2</sup>                      | LBD <sub>RES</sub>   |                                                                                                           | _       | 50   | _   | mV     |

| Low Battery Detector<br>Conversion Time <sup>2</sup>                 | LBD <sub>CT</sub>    |                                                                                                           | _       | 250  | _   | μs     |

| Microcontroller Clock<br>Output Frequency                            | F <sub>MC</sub>      | Configurable to 30 MHz,<br>15 MHz, 10 MHz, 4 MHz,<br>3 MHz, 2 MHz, 1 MHz, or<br>32.768 kHz                | 32.768K | _    | 30M | Hz     |

| General Purpose ADC Resolution <sup>2</sup>                          | ADC <sub>ENB</sub>   |                                                                                                           | _       | 8    | _   | bit    |

| General Purpose ADC Bit<br>Resolution <sup>2</sup>                   | ADC <sub>RES</sub>   |                                                                                                           | _       | 4    | _   | mV/bit |

| Temp Sensor & General<br>Purpose ADC Conversion<br>Time <sup>2</sup> | ADC <sub>CT</sub>    |                                                                                                           | _       | 305  |     | μs     |

| 30 MHz XTAL Start-Up time                                            | t <sub>30M</sub>     | Using XTAL and board layout in reference design. Start-up time will vary with XTAL type and board layout. | _       | 600  | _   | μs     |

| 30 MHz XTAL Cap<br>Resolution <sup>2</sup>                           | 30M <sub>RES</sub>   |                                                                                                           | _       | 97   | _   | fF     |

| 32 kHz XTAL Start-Up Time <sup>2</sup>                               | t <sub>32k</sub>     |                                                                                                           | _       | 6    | _   | sec    |

| 32 kHz XTAL Accuracy<br>using 32 kHz XTAL <sup>2</sup>               | 32K <sub>RES</sub>   | Using 20 ppm 32 kHz Crystal                                                                               | _       | 100  | _   | ppm    |

| 32 kHz Accuracy using Internal RC Oscillator <sup>2</sup>            | 32KRC <sub>RES</sub> |                                                                                                           | _       | 2500 | _   | ppm    |

| POR Reset Time                                                       | t <sub>POR</sub>     |                                                                                                           | _       | 16   | _   | ms     |

| Software Reset Time <sup>2</sup>                                     | t <sub>soft</sub>    |                                                                                                           | _       | 100  | _   | μs     |

- 1. All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

- **2.** Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

Table 5. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and nIRQ)

| Parameter                          | Symbol            | Conditions                                                      | Min                   | Тур | Max | Units |

|------------------------------------|-------------------|-----------------------------------------------------------------|-----------------------|-----|-----|-------|

| Rise Time                          | T <sub>RISE</sub> | $0.1 \times V_{DD}$ to $0.9 \times V_{DD}$ , $C_L = 5 pF$       | _                     | _   | 8   | ns    |

| Fall Time                          | T <sub>FALL</sub> | $0.9 \text{ x V}_{DD}$ to $0.1 \text{ x V}_{DD}$ , $C_L$ = 5 pF | _                     | _   | 8   | ns    |

| Input Capacitance                  | $C_{IN}$          |                                                                 |                       | _   | 1   | pF    |

| Logic High Level Input Voltage     | $V_{IH}$          |                                                                 | V <sub>DD</sub> – 0.6 | _   |     | V     |

| Logic Low Level Input Voltage      | V <sub>IL</sub>   |                                                                 |                       | _   | 0.6 | V     |

| Input Current                      | I <sub>IN</sub>   | 0 <v<sub>IN&lt; V<sub>DD</sub></v<sub>                          | -100                  | _   | 100 | nA    |

| Logic High Level Output<br>Voltage | V <sub>OH</sub>   | I <sub>OH</sub> <1 mA source, V <sub>DD</sub> =1.8 V            | V <sub>DD</sub> – 0.6 | _   | _   | V     |

| Logic Low Level Output Voltage     | V <sub>OL</sub>   | I <sub>OL</sub> <1 mA sink, V <sub>DD</sub> =1.8 V              | _                     | _   | 0.6 | ٧     |

**Note:** All specifications guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

Table 6. GPIO Specifications (GPIO\_0, GPIO\_1, and GPIO\_2)

| Parameter                            | Symbol              | Conditions                                                              | Min                   | Тур | Max | Units |

|--------------------------------------|---------------------|-------------------------------------------------------------------------|-----------------------|-----|-----|-------|

| Rise Time                            | T <sub>RISE</sub>   | $0.1 \times V_{DD}$ to $0.9 \times V_{DD}$ , $C_L$ = 10 pF, DRV<1:0>=HH | _                     | _   | 8   | ns    |

| Fall Time                            | T <sub>FALL</sub>   | $0.9 \times V_{DD}$ to $0.1 \times V_{DD}$ , $C_L$ = 10 pF, DRV<1:0>=HH | _                     | _   | 8   | ns    |

| Input Capacitance                    | C <sub>IN</sub>     |                                                                         | _                     | _   | 1   | pF    |

| Logic High Level Input Voltage       | V <sub>IH</sub>     |                                                                         | V <sub>DD</sub> – 0.6 | _   |     | V     |

| Logic Low Level Input Voltage        | $V_{IL}$            |                                                                         | _                     | _   | 0.6 | V     |

| Input Current                        | I <sub>IN</sub>     | $0 < V_{IN} < V_{DD}$                                                   | -100                  | _   | 100 | nA    |

| Input Current If Pullup is Activated | I <sub>INP</sub>    | V <sub>IL</sub> =0 V                                                    | 5                     | _   | 25  | μΑ    |

| Maximum Output Current               | I <sub>OmaxLL</sub> | DRV<1:0>=LL                                                             | 0.1                   | 0.5 | 8.0 | mA    |

|                                      | I <sub>OmaxLH</sub> | DRV<1:0>=LH                                                             | 0.9                   | 2.3 | 3.5 | mA    |

|                                      | I <sub>OmaxHL</sub> | DRV<1:0>=HL                                                             | 1.5                   | 3.1 | 4.8 | mA    |

|                                      | I <sub>OmaxHH</sub> | DRV<1:0>=HH                                                             | 1.8                   | 3.6 | 5.4 | mA    |

| Logic High Level Output Voltage      | V <sub>OH</sub>     | I <sub>OH</sub> < I <sub>Omax</sub> source,<br>V <sub>DD</sub> =1.8 V   | V <sub>DD</sub> – 0.6 | _   | _   | V     |

| Logic Low Level Output Voltage       | V <sub>OL</sub>     | I <sub>OL</sub> < I <sub>Omax</sub> sink,<br>V <sub>DD</sub> =1.8 V     |                       | _   | 0.6 | V     |

**Note:** All specifications guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

## Si4030/31/32-B1

**Table 7. Absolute Maximum Ratings**

| Parameter                                                  | Value                       | Unit |

|------------------------------------------------------------|-----------------------------|------|

| V <sub>DD</sub> to GND                                     | -0.3, +3.6                  | V    |

| Instantaneous V <sub>RF-peak</sub> to GND on TX Output Pin | -0.3, +8.0                  | V    |

| Sustained V <sub>RF-peak</sub> to GND on TX Output Pin     | -0.3, +6.5                  | V    |

| Voltage on Digital Control Inputs                          | -0.3, V <sub>DD</sub> + 0.3 | V    |

| Voltage on Analog Inputs                                   | -0.3, V <sub>DD</sub> + 0.3 | V    |

| Operating Ambient Temperature Range T <sub>A</sub>         | -40 to +85                  | °C   |

| Thermal Impedance $\theta_{JA}$                            | 30                          | °C/W |

| Junction Temperature T <sub>J</sub>                        | +125                        | °C   |

| Storage Temperature Range T <sub>STG</sub>                 | -55 to +125                 | °C   |

**Note:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at or beyond these ratings in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Power Amplifier may be damaged if switched on without proper load or termination connected. TX matching network design will influence TX V<sub>RF-peak</sub> on TX output pin. Caution: ESD sensitive device.

## 1.1. Definition of Test Conditions

## **Production Test Conditions:**

- T<sub>A</sub> = +25 °C

- V<sub>DD</sub> = +3.3 VDC

- TX output power measured at 915 MHz

- External reference signal (XOUT) = 1.0 V<sub>PP</sub> at 30 MHz, centered around 0.8 VDC

- Production test schematic (unless noted otherwise)

- All RF output levels referred to the pins of the Si4030/31/32 (not the RF module)

## **Qualification Test Conditions:**

- $T_A = -40 \text{ to } +85 \text{ }^{\circ}\text{C}$

- $V_{DD}$  = +1.8 to +3.6 VDC

- Using 4032, 4031, or 4030 reference design or production test schematic

- All RF output levels referred to the pins of the Si4030/31/32 (not the RF module)

## 2. Functional Description

The Si4030/31/32 are ISM wireless transmitters with continuous frequency tuning over their specified bands which encompasses 240–960 MHz. The wide operating voltage range of 1.8–3.6 V and low current consumption makes the Si4030/31/32 an ideal solution for battery powered applications.

The RF carrier is generated by an integrated VCO and  $\Delta\Sigma$  Fractional-N PLL synthesizer. The synthesizer is designed to support configurable data rates, output frequency, frequency deviation, and Gaussian filtering at any frequency between 240–960 MHz. The transmit FSK data is modulated directly into the  $\Delta\Sigma$  data stream and can be shaped by a Gaussian low-pass filter to reduce unwanted spectral content.

The Si4032's PA output power can be configured between +1 and +20 dBm in 3 dB steps, while the Si4030/31's PA output power can be configured between –8 and +13 dBm in 3 dB steps. The PA is single-ended to allow for easy antenna matching and low BOM cost. The PA incorporates automatic ramp-up and ramp-down control to reduce unwanted spectral spreading. The +20 dBm power amplifier of the Si4032 can also be used to compensate for the reduced performance of a lower cost, lower performance antenna or antenna with size constraints due to a small form-factor. Competing solutions require large and expensive external PAs to achieve comparable performance.

The Si4030/31/32 is designed to work with a microcontroller, crystal, and a few external components to create a very low cost system. Voltage regulators are integrated on-chip which allows for a wide operating supply voltage range from +1.8 to +3.6 V. A standard 4-pin SPI bus is used to communicate with an external microcontroller. Three configurable general purpose I/Os are available. A complete list of the available GPIO functions is available in "AN466: Si4030/31/32 Register Descriptions."

## 2.1. Operating Modes

The Si4030/31/32 provides several operating modes which can be used to optimize the power consumption for a given application.

Table 8 summarizes the operating modes of the Si4030/31/32. In general, any given operating mode may be classified as an active mode or a power saving mode. The table indicates which block(s) are enabled (active) in each corresponding mode. With the exception of the SHUTDOWN mode, all can be dynamically selected by sending the appropriate commands over the SPI. An "X" in any cell means that, in the given mode of operation, that block can be independently programmed to be either ON or OFF, without noticeably impacting the current consumption. The SPI circuit block includes the SPI interface hardware and the device register space. The 32 kHz OSC block includes the 32.768 kHz RC oscillator or 32.768 kHz crystal oscillator and wake-up timer. AUX (Auxiliary Blocks) includes the temperature sensor, general purpose ADC, and low-battery detector.

**Circuit Blocks Mode Name Digital LDO** SPI 32 kHz OSC **AUX** 30 MHz **PLL** PA  $I_{VDD}$ **XTAL** OFF OFF SHUTDOWN OFF OFF **OFF OFF OFF** 15 nA (Register contents lost) ON **OFF STANDBY** ON OFF **OFF** OFF **OFF** 450 nA SLEEP (Register contents OFF ON ON OFF OFF  $1 \, \mu A$ Χ retained) **SENSOR** ON Χ ON OFF OFF OFF 1 µA **READY** ON Χ Χ OFF **OFF** ON 800 μΑ OFF **TUNING** ON Χ Χ 8.5 mA ON ON TRANSMIT ON X Χ ON ON ON 30 mA\*

**Table 8. Operating Modes**

\*Note: Using Si4030/31 at +13 dBm using recommended reference design.

## 3. Controller Interface

## 3.1. Serial Peripheral Interface (SPI)

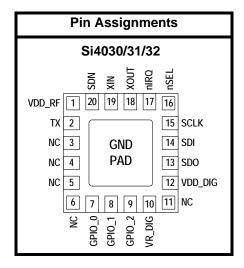

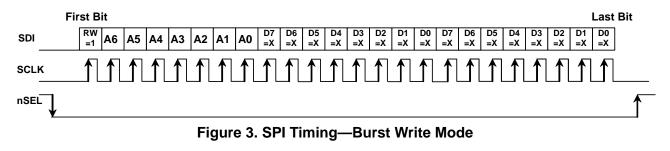

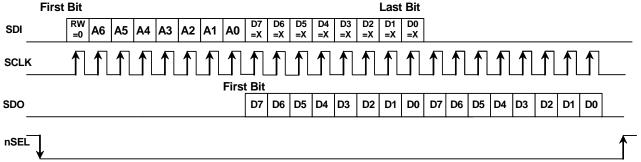

The Si4030/31/32 communicates with the host MCU over a standard 3-wire SPI interface: SCLK, SDI, and nSEL. The host MCU can read data from the device on the SDO output pin. A SPI transaction is a 16-bit sequence which consists of a Read-Write ( $\overline{R}$ /W) select bit, followed by a 7-bit address field (ADDR), and an 8-bit data field (DATA) as demonstrated in Figure 1. The 7-bit address field is used to select one of the 128, 8-bit control registers. The  $\overline{R}$ /W select bit determines whether the SPI transaction is a read or write transaction. If  $\overline{R}$ /W = 1 it signifies a WRITE transaction, while  $\overline{R}$ /W = 0 signifies a READ transaction. The contents (ADDR or DATA) are latched into the Si4030/31/32 every eight clock cycles. The timing parameters for the SPI interface are shown in Table 9. The SCLK rate is flexible with a maximum rate of 10 MHz.

Figure 1. SPI Timing

**Table 9. Serial Interface Timing Parameters**

| Symbol          | Parameter              | Min (nsec) | Diagram                                     |

|-----------------|------------------------|------------|---------------------------------------------|

| t <sub>CH</sub> | Clock high time        | 40         |                                             |

| t <sub>CL</sub> | Clock low time         | 40         | SCLK / / / / / / / / / / / / / / / / / / /  |

| t <sub>DS</sub> | Data setup time        | 20         | tss tcl tan tos ton too tsn toe             |

| t <sub>DH</sub> | Data hold time         | 20         |                                             |

| t <sub>DD</sub> | Output data delay time | 20         | SDI XX                                      |

| t <sub>EN</sub> | Output enable time     | 20         | SDO TEN |

| t <sub>DE</sub> | Output disable time    | 50         |                                             |

| t <sub>SS</sub> | Select setup time      | 20         | nSEL 1    /                                 |

| t <sub>SH</sub> | Select hold time       | 50         |                                             |

| t <sub>SW</sub> | Select high period     | 80         |                                             |

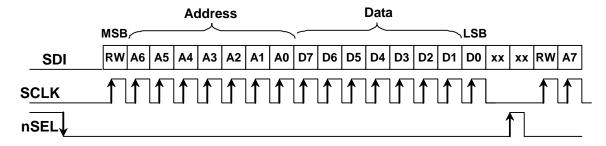

To read back data from the Si4030/31/32, the R/W bit must be set to 0 followed by the 7-bit address of the register from which to read. The 8 bit DATA field following the 7-bit ADDR field is ignored n the SDI pin when R/W = 0. The next eight negative edge transitions of the SCLK signal will clock out the contents of the selected register. The data read from the selected register will be available on the SDO output pin. The READ function is shown in Figure 2. After the READ function is completed the SDO pin will remain at either a logic 1 or logic 0 state depending on the last data bit clocked out (D0). When nSEL goes high the SDO output pin will be pulled high by internal pullup.

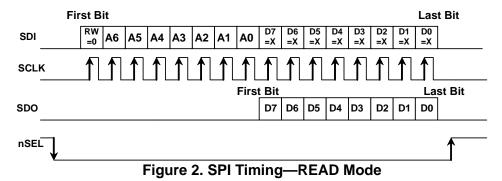

The SPI interface contains a burst read/write mode which allows for reading/writing sequential registers without having to re-send the SPI address. When the nSEL bit is held low while continuing to send SCLK pulses, the SPI interface will automatically increment the ADDR and read from/write to the next address. An example burst write transaction is illustrated in Figure 3 and a burst read in Figure 4. As long as nSEL is held low, input data will be latched into the Si4030/31/32 every eight SCLK cycles.

Figure 4. SPI Timing—Burst Read Mode

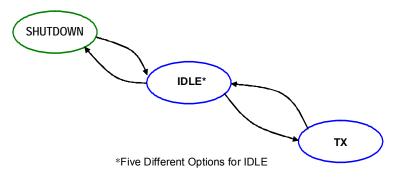

## 3.2. Operating Mode Control

There are three primary states in the Si4030/31/32 radio state machine: SHUTDOWN, IDLE, and TX (see Figure 5). The SHUTDOWN state completely shuts down the radio to minimize current consumption. There are five different configurations/options for the IDLE state which can be selected to optimize the chip to the applications needs. "Register 07h. Operating Mode and Function Control 1" controls which operating mode/state is selected with the exception of SHUTDOWN which is controlled by SDN pin 20. The TX state may be reached automatically from any of the IDLE states by setting the txon bit in "Register 07h. Operating Mode and Function Control 1." Table 10 shows each of the operating modes with the time required to reach TX mode as well as the current consumption of each mode.

The Si4030/31/32 includes a low-power digital regulated supply (LPLDO) which is internally connected in parallel to the output of the main digital regulator (and is available externally at the VR\_DIG pin). This common digital supply voltage is connected to all digital circuit blocks including the SPI and register space. The LPLDO has extremely low quiescent current consumption but limited current supply capability; it is used only in the IDLE-STANDBY and IDLE-SLEEP modes. The main digital regulator is automatically enabled in all other modes.

Figure 5. State Machine Diagram

**Table 10. Operating Modes Response Time**

| State/Mode                                                            | Response Time to TX                            | Current in State/Mode [μΑ]                                   |

|-----------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------|

| Shut Down State                                                       | 16.8 ms                                        | 15 nA                                                        |

| Idle States: Standby Mode Sleep Mode Sensor Mode Ready Mode Tune Mode | 800 µs<br>800 µs<br>800 µs<br>200 µs<br>200 µs | 450 nA<br>1 μA<br>1 μA<br>800 μA<br>8.5 mA                   |

| TX State                                                              | NA                                             | Si4032:<br>85 mA @ +20 dBm,<br>Si4030/31:<br>30 mA @ +13 dBm |

## Si4030/31/32-B1

#### 3.2.1. SHUTDOWN State

The SHUTDOWN state is the lowest current consumption state of the device with nominally less than 15 nA of current consumption. The SHUTDOWN state may be entered by driving the SDN pin (Pin 20) high. The SDN pin should be held low in all states except the SHUTDOWN state. In the SHUTDOWN state, the contents of the registers are lost and there is no SPI access.

When the chip is connected to the power supply, a POR will be initiated after the falling edge of SDN.

#### 3.2.2. IDLE State

There are five different modes in the IDLE state which may be selected by "Register 07h. Operating Mode and Function Control 1". All modes have a tradeoff between current consumption and response time to TX mode. This tradeoff is shown in Table 10. After the POR event, SWRESET, or exiting from the SHUTDOWN state the chip will default to the IDLE-READY mode. After a POR event the interrupt registers must be read to properly enter the SLEEP, SENSOR, or STANDBY mode and to control the 32 kHz clock correctly.

#### 3.2.2.1. STANDBY Mode

STANDBY mode has the lowest current consumption of the five IDLE states with only the LPLDO enabled to maintain the register values. In this mode the registers can be accessed in both read and write mode. The STANDBY mode can be entered by writing 0h to "Register 07h. Operating Mode and Function Control 1". If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption. Additionally, the ADC should not be selected as an input to the GPIO in this mode as it will cause excess current consumption.

#### 3.2.2.2. SLEEP Mode

In SLEEP mode the LPLDO is enabled along with the Wake-Up-Timer, which can be used to accurately wake-up the radio at specified intervals. See "7.6. Wake-Up Timer" on page 45 for more information on the Wake-Up-Timer. SLEEP mode is entered by setting enwt = 1 (40h) in "Register 07h. Operating Mode and Function Control 1". If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption. Also, the ADC should not be selected as an input to the GPIO in this mode as it will cause excess current consumption.

#### 3.2.2.3. SENSOR Mode

In SENSOR Mode either the Low Battery Detector, Temperature Sensor, or both may be enabled in addition to the LPLDO and Wake-Up-Timer. The Low Battery Detector can be enabled by setting enlbd = 1 in "Register 07h. Operating Mode and Function Control 1". See "7.4. Temperature Sensor" on page 42 and "7.5. Low Battery Detector" on page 44 for more information on these features. If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption.

#### 3.2.2.4. READY Mode

READY Mode is designed to give a fast transition time to TX mode with reasonable current consumption. In this mode the Crystal oscillator remains enabled reducing the time required to switch to TX mode by eliminating the crystal start-up time. READY mode is entered by setting xton = 1 in "Register 07h. Operating Mode and Function Control 1". To achieve the lowest current consumption state the crystal oscillator buffer should be disabled in "Register 62h. Crystal Oscillator Control and Test."

#### 3.2.2.5. TUNE Mode

In TUNE Mode the PLL remains enabled in addition to the other blocks enabled in the IDLE modes. This will give the fastest response to TX mode as the PLL will remain locked but it results in the highest current consumption. This mode of operation is designed for frequency hopping spread spectrum systems (FHSS). TUNE mode is entered by setting pllon = 1 in "Register 07h. Operating Mode and Function Control 1". It is not necessary to set xton to 1 for this mode, the internal state machine automatically enables the crystal oscillator.

#### 3.2.3. TX State

The TX state may be entered from any of the IDLE modes when the txon bit is set to 1 in "Register 07h. Operating Mode and Function Control 1". A built-in sequencer takes care of all the actions required to transition between states from enabling the crystal oscillator to ramping up the PA. The following sequence of events will occur automatically when going from STANDBY mode to TX mode by setting the txon bit.

- 1. Enable the main digital LDO and the Analog LDOs.

- 2. Start up crystal oscillator and wait until ready (controlled by an internal timer).

- 3. Enable PLL.

- 4. Calibrate VCO (this action is skipped when the vcocal bit is "0", default value is "1").

- 5. Wait until PLL settles to required transmit frequency (controlled by timer).

- 6. Activate power amplifier and wait until power ramping is completed (controlled by an internal timer).

- 7. Transmit packet.

Steps in this sequence may be eliminated depending on which IDLE mode the chip is configured to prior to setting the txon bit. By default, the VCO and PLL are calibrated every time the PLL is enabled.

#### 3.2.4. Device Status

| Add | R/W | Function/Description | D7     | D6     | D5       | D4       | D3      | D2 | D1     | D0     | POR Def. |

|-----|-----|----------------------|--------|--------|----------|----------|---------|----|--------|--------|----------|

| 02  | R   | Device Status        | ffovfl | ffunfl | Reserved | Reserved | freqerr |    | cps[1] | cps[0] | _        |

The operational status of the chip can be read from "Register 02h. Device Status".

## 3.3. Interrupts

The Si4030/31/32 is capable of generating an interrupt signal when certain events occur. The chip notifies the microcontroller that an interrupt event has occurred by setting the nIRQ output pin LOW = 0. This interrupt signal will be generated when any one (or more) of the interrupt events (corresponding to the Interrupt Status bits) shown below occur. The nIRQ pin will remain low until the microcontroller reads the Interrupt Status Register(s) (Registers 03h–04h) containing the active Interrupt Status bit. The nIRQ output signal will then be reset until the next change in status is detected. The interrupts must be enabled by the corresponding enable bit in the Interrupt Enable Registers (Registers 05h–06h). All enabled interrupt bits will be cleared when the microcontroller reads the interrupt status register. If the interrupt is not enabled when the event occurs it will not trigger the nIRQ pin, but the status may still be read at anytime in the Interrupt Status registers.

| Add | R/W | Function/Descript ion | D7       | D6          | D5        | D4       | D3    | D2       | D1        | D0       | POR Def. |

|-----|-----|-----------------------|----------|-------------|-----------|----------|-------|----------|-----------|----------|----------|

| 03  | R   | Interrupt Status 1    | ifferr   | itxffafull  | itxffaem  | Reserved | iext  | ipksent  | Reserved  | Reserved | _        |

| 04  | R   | Interrupt Status 2    | Reserved | Reserved    | Reserved  | Reserved | iwut  | ilbd     | ichiprdy  | ipor     | _        |

| 05  | R/W | Interrupt Enable 1    | enfferr  | entxffafull | entxffaem | Reserved | enext | enpksent | Reserved  | Reserved | 00h      |

| 06  | R/W | Interrupt Enable 2    | Reserved | Reserved    | Reserved  | Reserved | enwut | enlbd    | enchiprdy | enpor    | 01h      |

See "AN466: Si4030/31/32 Register Descriptions" for a complete list of interrupts.

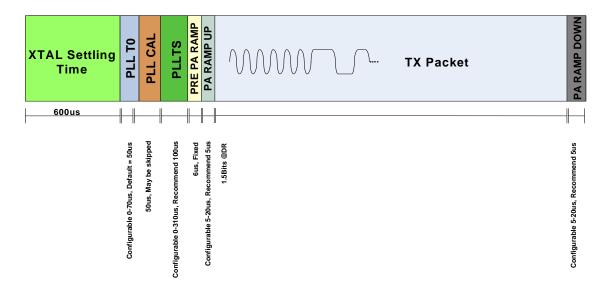

## 3.4. System Timing

The system timing for TX mode is shown in Figure 6. The figures demonstrate transitioning from STANDBY mode to TX mode through the built-in sequencer of required steps. The user only needs to program the desired mode, and the internal sequencer will properly transition the part from its current mode.

The VCO will automatically calibrate at every frequency change or power up. The PLL T0 time is to allow for bias settling of the VCO. The PLL TS time is for the settling time of the PLL, which has a default setting of 100  $\mu$ s. The total time for PLL T0, PLL CAL, and PLL TS under all conditions is 200  $\mu$ s. Under certain applications, the PLL T0 time and the PLL CAL may be skipped for faster turn-around time. Contact applications support if faster turnaround time is desired.

Figure 6. TX Timing

## 3.5. Frequency Control

For calculating the necessary frequency register settings it is recommended that customers use Silicon Labs' Wireless Design Suite (WDS) or the EZRadioPRO Register Calculator worksheet (in Microsoft Excel) available on the product website. These methods offer a simple method to quickly determine the correct settings based on the application requirements. The following information can be used to calculated these values manually.

## 3.5.1. Frequency Programming

In order to transmit an RF signal, the desired channel frequency,  $f_{carrier}$ , must be programmed into the Si4030/31/32. Note that this frequency is the center frequency of the desired channel. The carrier frequency is generated by a Fractional-N Synthesizer, using 10 MHz both as the reference frequency and the clock of the (3<sup>rd</sup> order)  $\Delta\Sigma$  modulator. This modulator uses modulo 64000 accumulators. This design was made to obtain the desired frequency resolution of the synthesizer. The overall division ratio of the feedback loop consist of an integer part (N) and a fractional part (F).In a generic sense, the output frequency of the synthesizer is as follows:

$$f_{OUT} = 10MHz \times (N+F)$$

The fractional part (F) is determined by three different values, Carrier Frequency (fc[15:0]), Frequency Offset (fo[8:0]), and Frequency Deviation (fd[7:0]). Due to the fine resolution and high loop bandwidth of the synthesizer, FSK modulation is applied inside the loop and is done by varying F according to the incoming data; this is discussed further in "3.5.4. Frequency Deviation" on page 24. Also, a fixed offset can be added to fine-tune the carrier frequency and counteract crystal tolerance errors. For simplicity assume that only the fc[15:0] register will determine the fractional component. The equation for selection of the carrier frequency is shown below:

$$\begin{split} f_{carrier} = &10MHz \times (hbsel + 1) \times (N + F) \\ f_{TX} = &10MHz * (hbsel + 1) * (fb[4:0] + 24 + \frac{fc[15:0]}{64000}) \end{split}$$

| Add | R/W | Function/Description           | D7     | D6     | D5     | D4     | D3     | D2     | D1    | D0    | POR Def. |

|-----|-----|--------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|----------|

| 73  | R/W | Frequency Offset 1             | fo[7]  | fo[6]  | fo[5]  | fo[4]  | fo[3]  | fo[2]  | fo[1] | fo[0] | 00h      |

| 74  | R/W | Frequency Offset 2             |        |        |        |        |        |        | fo[9] | fo[8] | 00h      |

| 75  | R/W | Frequency Band Select          |        | sbsel  | hbsel  | fb[4]  | fb[3]  | fb[2]  | fb[1] | fb[0] | 35h      |

| 76  | R/W | Nominal Carrier<br>Frequency 1 | fc[15] | fc[14] | fc[13] | fc[12] | fc[11] | fc[10] | fc[9] | fc[8] | BBh      |

| 77  | R/W | Nominal Carrier<br>Frequency 0 | fc[7]  | fc[6]  | fc[5]  | fc[4]  | fc[3]  | fc[2]  | fc[1] | fc[0] | 80h      |

The integer part (N) is determined by fb[4:0]. Additionally, the output frequency can be halved by connecting a  $\div 2$  divider to the output. This divider is not inside the loop and is controlled by the hbsel bit in "Register 75h. Frequency Band Select". This effectively partitions the entire 240–960 MHz frequency range into two separate bands: High Band (HB) for hbsel = 1, and Low Band (LB) for hbsel = 0. The valid range of fb[4:0] is from 0 to 23. If a higher value is written into the register, it will default to a value of 23. The integer part has a fixed offset of 24 added to it as shown in the formula above. Table 11 demonstrates the selection of fb[4:0] for the corresponding frequency band.

After selection of the fb (N) the fractional component may be solved with the following equation:

$$fc[15:0] = \left(\frac{f_{TX}}{10MHz*(hbsel+1)} - fb[4:0] - 24\right)*64000$$

fb and fc are the actual numbers stored in the corresponding registers.

**Table 11. Frequency Band Selection**

| fb[4:0] Value | N  | Frequen       | cy Band       |

|---------------|----|---------------|---------------|

|               |    | hbsel=0       | hbsel=1       |

| 0             | 24 | 240–249.9 MHz | 480–499.9 MHz |

| 1             | 25 | 250–259.9 MHz | 500–519.9 MHz |

| 2             | 26 | 260–269.9 MHz | 520–539.9 MHz |

| 3             | 27 | 270–279.9 MHz | 540–559.9 MHz |

| 4             | 28 | 280–289.9 MHz | 560–579.9 MHz |

| 5             | 29 | 290–299.9 MHz | 580–599.9 MHz |

| 6             | 30 | 300–309.9 MHz | 600–619.9 MHz |

| 7             | 31 | 310–319.9 MHz | 620–639.9 MHz |

| 8             | 32 | 320–329.9 MHz | 640–659.9 MHz |

| 9             | 33 | 330–339.9 MHz | 660–679.9 MHz |

| 10            | 34 | 340–349.9 MHz | 680–699.9 MHz |

| 11            | 35 | 350–359.9 MHz | 700–719.9 MHz |

| 12            | 36 | 360-369.9 MHz | 720–739.9 MHz |

| 13            | 37 | 370–379.9 MHz | 740–759.9 MHz |

| 14            | 38 | 380–389.9 MHz | 760–779.9 MHz |

| 15            | 39 | 390–399.9 MHz | 780–799.9 MHz |

| 16            | 40 | 400–409.9 MHz | 800–819.9 MHz |

| 17            | 41 | 410–419.9 MHz | 820-839.9 MHz |

| 18            | 42 | 420–429.9 MHz | 840-859.9 MHz |

| 19            | 43 | 430–439.9 MHz | 860–879.9 MHz |

| 20            | 44 | 440–449.9 MHz | 880–899.9 MHz |

| 21            | 45 | 450–459.9 MHz | 900–919.9 MHz |

| 22            | 46 | 460–469.9 MHz | 920–939.9 MHz |

| 23            | 47 | 470–479.9 MHz | 940–960 MHz   |

#### 3.5.2. Easy Frequency Programming for FHSS

While Registers 73h–77h may be used to program the carrier frequency of the Si4030/31/32, it is often easier to think in terms of "channels" or "channel numbers" rather than an absolute frequency value in Hz. Also, there may be some timing-critical applications (such as for Frequency Hopping Systems) in which it is desirable to change frequency by programming a single register. Once the channel step size is set, the frequency may be changed by a single register corresponding to the channel number. A nominal frequency is first set using Registers 73h–77h, as described above. Registers 79h and 7Ah are then used to set a channel step size and channel number, relative to the nominal setting. The Frequency Hopping Step Size (fhs[7:0]) is set in increments of 10 kHz with a maximum channel step size of 2.56 MHz. The Frequency Hopping Channel Select Register then selects channels based on multiples of the step size.

$$F_{carrier} = Fnom + fhs[7:0] \times (fhch[7:0] \times 10kHz)$$

For example, if the nominal frequency is set to 900 MHz using Registers 73h–77h, the channel step size is set to 1 MHz using "Register 7Ah. Frequency Hopping Step Size," and "Register 79h. Frequency Hopping Channel Select" is set to 5d, the resulting carrier frequency would be 905 MHz. Once the nominal frequency and channel step size are programmed in the registers, it is only necessary to program the fhch[7:0] register in order to change the frequency.

| Add | R/W | Function/Description                | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      | POR Def. |

|-----|-----|-------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|----------|

| 79  | R/W | Frequency Hopping Channel<br>Select | fhch[7] | fhch[6] | fhch[5] | fhch[4] | fhch[3] | fhch[2] | fhch[1] | fhch[0] | 00h      |

| 7A  | R/W | Frequency Hopping Step<br>Size      | fhs[7]  | fhs[6]  | fhs[5]  | fhs[4]  | fhs[3]  | fhs[2]  | fhs[1]  | fhs[0]  | 00h      |

#### 3.5.3. Automatic State Transition for Frequency Change

If registers 79h or 7Ah are changed in TX mode, the state machine will automatically transition the chip back to TUNE and change the frequency. This feature is useful to reduce the number of SPI commands required in a Frequency Hopping System. This in turn reduces microcontroller activity, reducing current consumption. The exception to this is during TX FIFO mode. If a frequency change is initiated during a TX packet, then the part will complete the current TX packet and will only change the frequency for subsequent packets.

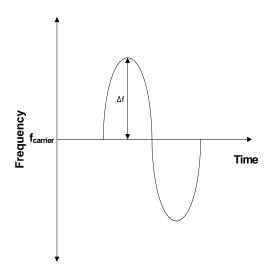

## 3.5.4. Frequency Deviation

The peak frequency deviation is configurable from  $\pm 0.625$  to  $\pm 320$  kHz. The Frequency Deviation ( $\Delta f$ ) is controlled by the Frequency Deviation Register (fd), address 71 and 72h, and is independent of the carrier frequency setting. When enabled, regardless of the setting of the hbsel bit (high band or low band), the resolution of the frequency deviation will remain in increments of 625 Hz. When using frequency modulation the carrier frequency will deviate from the nominal center channel carrier frequency by  $\pm \Delta f$ :

$$\Delta f = fd[8:0] \times 625Hz$$

$$fd[8:0] = \frac{\Delta f}{625Hz} \quad \Delta f = \text{peak deviation}$$

Figure 7. Frequency Deviation

The previous equation should be used to calculate the desired frequency deviation. If desired, frequency modulation may also be disabled in order to obtain an unmodulated carrier signal at the channel center frequency; see "4.1. Modulation Type" on page 27 for further details.

| Add | R/W | Function/Description      | D7       | D6       | D5       | D4       | D3    | D2    | D1        | D0        | POR Def. |

|-----|-----|---------------------------|----------|----------|----------|----------|-------|-------|-----------|-----------|----------|

| 71  | R/W | Modulation Mode Control 2 | trclk[1] | trclk[0] | dtmod[1] | dtmod[0] | eninv | fd[8] | modtyp[1] | modtyp[0] | 00h      |

| 72  | R/W | Frequency Deviation       | fd[7]    | fd[6]    | fd[5]    | fd[4]    | fd[3] | fd[2] | fd[1]     | fd[0]     | 20h      |

### 3.5.5. Frequency Offset Adjustment

A frequency offset can be adjusted manually by fo[9:0] in registers 73h and 74h. The frequency offset adjustment is implemented by shifting the Synthesizer Local Oscillator frequency. This register is a signed register so in order to get a negative offset it is necessary to take the twos complement of the positive offset number. The offset can be calculated by the following:

$$DesiredOffset = 156.25Hz \times (hbsel + 1) \times fo[9:0]$$

$$fo[9:0] = \frac{DesiredOffset}{156.25Hz \times (hbsel + 1)}$$

The adjustment range in high band is ±160 kHz and in low band it is ±80 kHz. For example to compute an offset of +50 kHz in high band mode fo[9:0] should be set to 0A0h. For an offset of –50 kHz in high band mode the fo[9:0] register should be set to 360h.

| Add | R/W | Function/Descript ion | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    | POR<br>Def. |

|-----|-----|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------|

| 73  | R/W | Frequency Offset      | fo[7] | fo[6] | fo[5] | fo[4] | fo[3] | fo[2] | fo[1] | fo[0] | 00h         |

| 74  | R/W | Frequency Offset      |       |       |       |       |       |       | fo[9] | fo[8] | 00h         |

#### 3.5.6. TX Data Rate Generator

The data rate is configurable between 0.123–256 kbps. For data rates below 30 kbps the "txdtrtscale" bit in register 70h should be set to 1. When higher data rates are used this bit should be set to 0.

The TX date rate is determined by the following formula in kbps:

$$DR\_TX \text{ (kbps)} = \frac{txdr[15:0] \times 1 \text{ MHz}}{2^{16+5 \times txdtrtscale}}$$

$$txdr[15:0] \ = \ \frac{DR\_TX(kbps) \times 2^{16 + 5 \times txdtrtscale}}{1 \ MHz}$$

| Add | R/W | Function/Description | D7       | D6       | D5       | D4       | D3       | D2       | D1      | D0      | POR Def. |

|-----|-----|----------------------|----------|----------|----------|----------|----------|----------|---------|---------|----------|

| 6E  | R/W | TX Data Rate 1       | txdr[15] | txdr[14] | txdr[13] | txdr[12] | txdr[11] | txdr[10] | txdr[9] | txdr[8] | 0Ah      |

| 6F  | R/W | TX Data Rate 0       | txdr[7]  | txdr[6]  | txdr[5]  | txdr[4]  | txdr[3]  | txdr[2]  | txdr[1] | txdr[0] | AAh      |

## 4. Modulation Options

## 4.1. Modulation Type

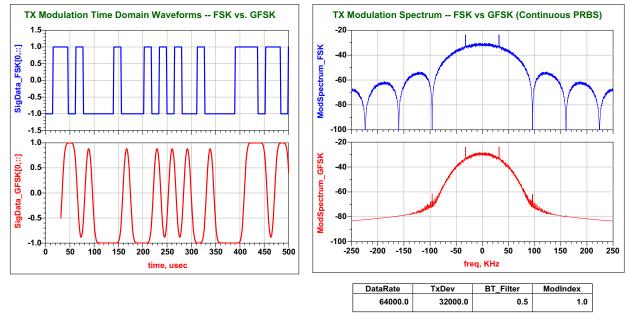

The Si4030/31/32 supports three different modulation options: Gaussian Frequency Shift Keying (GFSK), Frequency Shift Keying (FSK), and On-Off Keying (OOK). GFSK is the recommended modulation type as it provides the best performance and cleanest modulation spectrum. Figure 8 demonstrates the difference between FSK and GFSK for a Data Rate of 64 kbps. The time domain plots demonstrate the effects of the Gaussian filtering. The frequency domain plots demonstrate the spectral benefit of GFSK over FSK. The type of modulation is selected with the modtyp[1:0] bits in "Register 71h. Modulation Mode Control 2." Note that it is also possible to obtain an unmodulated carrier signal by setting modtyp[1:0] = 00.

| modtyp[1:0] | Modulation Source                                  |

|-------------|----------------------------------------------------|

| 00          | Unmodulated Carrier                                |

| 01          | оок                                                |

| 10          | FSK                                                |

| 11          | GFSK (enable TX Data CLK when direct mode is used) |

Figure 8. FSK vs. GFSK Spectrums

#### 4.2. Modulation Data Source

The Si4030/31/32 may be configured to obtain its modulation data from one of three different sources: FIFO mode, Direct Mode, and from a PN9 mode. In Direct Mode, the TX modulation data may be obtained from several different input pins. These options are set through the dtmod[1:0] field in "Register 71h. Modulation Mode Control 2."

| Add | R/W | Function/Description         | D7       | D6       | D5       | D4       | D3    | D2    | D1        | D0        | POR Def. |

|-----|-----|------------------------------|----------|----------|----------|----------|-------|-------|-----------|-----------|----------|

| 71  | R/W | Modulation Mode<br>Control 2 | trclk[1] | trclk[0] | dtmod[1] | dtmod[0] | eninv | fd[8] | modtyp[1] | modtyp[0] | 00h      |

| dtmod[1:0] | Data Source                                                          |

|------------|----------------------------------------------------------------------|

| 00         | Direct Mode using TX Data via GPIO pin (GPIO configuration required) |

| 01         | Direct Mode using TX Data via SDI pin (only when nSEL is high)       |

| 10         | FIFO Mode                                                            |

| 11         | PN9 (internally generated)                                           |

#### 4.2.1. FIFO Mode

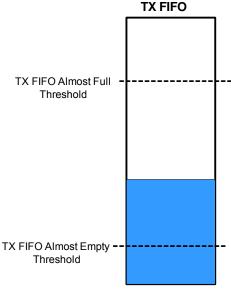

In FIFO mode, the transmit data is stored in integrated FIFO register memory. The FIFOs are accessed via "Register 7Fh. FIFO Access," and are most efficiently accessed with burst read/write operation as discussed in "3.1. Serial Peripheral Interface (SPI)" on page 15.

In TX mode, the data bytes stored in FIFO memory are "packaged" together with other fields and bytes of information to construct the final transmit packet structure. These other potential fields include the Preamble, Sync word, Header, CRC checksum, etc. The configuration of the packet structure in TX mode is determined by the Automatic Packet Handler (if enabled), in conjunction with a variety of Packet Handler Registers (see Table 12 on page 36). If the Automatic Packet Handler is disabled, the entire desired packet structure should be loaded into FIFO memory; no other fields (such as Preamble or Sync word are automatically added to the bytes stored in FIFO memory). For further information on the configuration of the FIFOs for a specific application or packet size, see "6. Data Handling and Packet Handler" on page 34.

When in FIFO mode, the chip will automatically exit the TX State when either the ipksent or ipkvalid interrupt occurs. The chip will return to the IDLE mode state programmed in "Register 07h. Operating Mode and Function Control 1". For example, the chip may be placed into TX mode by setting the txon bit, but with the pllon bit additionally set. The chip will transmit all of the contents of the FIFO and the ipksent interrupt will occur. When this interrupt event occurs, the chip will clear the txon bit and return to TUNE mode, as indicated by the set state of the pllon bit. If no other bits are additionally set in register 07h (besides txon initially), then the chip will return to the STANDBY state.

#### 4.2.2. Direct Mode

For legacy systems that perform packet handling within an MCU or other baseband chip, it may not be desirable to use the FIFO. For this scenario, a Direct Mode is provided which bypasses the FIFOs entirely.

In TX direct mode, the TX modulation data is applied to an input pin of the chip and processed in "real time" (i.e., not stored in a register for transmission at a later time). A variety of pins may be configured for use as the TX Data input function.

Furthermore, an additional pin may be required for a TX Clock output function if GFSK modulation is desired (only the TX Data input pin is required for FSK). Two options for the source of the TX Data are available in the dtmod[1:0] field, and various configurations for the source of the TX Data Clock may be selected through the trclk[1:0] field.

| trclk[1:0] | TX Data Clock Configuration                                                      |

|------------|----------------------------------------------------------------------------------|

| 00         | No TX Clock (only for FSK)                                                       |

| 01         | TX Data Clock is available via GPIO (GPIO needs programming accordingly as well) |

| 10         | TX Data Clock is available via SDO pin (only when nSEL is high)                  |

| 11         | TX Data Clock is available via the nIRQ pin                                      |

The eninv bit in SPI Register 71h will invert the TX Data; this is most likely useful for diagnostic and testing purposes.

#### 4.2.2.1. Direct Synchronous Mode

In TX direct mode, the chip may be configured for synchronous or asynchronous modes of modulation. In direct synchronous mode, the RFIC is configured to provide a TX Clock signal as an output to the external device that is providing the TX Data stream. This TX Clock signal is a square wave with a frequency equal to the programmed data rate. The external modulation source (e.g., MCU) must accept this TX Clock signal as an input and respond by providing one bit of TX Data back to the RFIC, synchronous with one edge of the TX Clock signal. In this fashion, the rate of the TX Data input stream from the external source is controlled by the programmed data rate of the RFIC; no TX Data bits are made available at the input of the RFIC until requested by another cycle of the TX Clock signal. The TX Data bits supplied by the external source are transmitted directly in real-time (i.e., not stored internally for later transmission).

All modulation types (FSK/GFSK/OOK) are valid in TX direct synchronous mode. As will be discussed in the next section, there are limits on modulation types in TX direct asynchronous mode.

#### 4.2.2.2. Direct Asynchronous Mode

In TX direct asynchronous mode, the RFIC no longer controls the data rate of the TX Data input stream. Instead, the data rate is controlled only by the external TX Data source; the RFIC simply accepts the data applied to its TX Data input pin, at whatever rate it is supplied. This means that there is no longer a need for a TX Clock output signal from the RFIC, as there is no synchronous "handshaking" between the RFIC and the external data source. The TX Data bits supplied by the external source are transmitted directly in real-time (i.e., not stored internally for later transmission).

It is not necessary to program the data rate parameter when operating in TX direct asynchronous mode. The chip still internally samples the incoming TX Data stream to determine when edge transitions occur; however, rather than sampling the data at a pre-programmed data rate, the chip now internally samples the incoming TX Data stream at its maximum possible oversampling rate. This allows the chip to accurately determine the timing of the bit edge transitions without prior knowledge of the data rate. (Of course, it is still necessary to program the desired peak frequency deviation.)

Only FSK and OOK modulation types are valid in TX Direct Asynchronous Mode; GFSK modulation is not available in asynchronous mode. This is because the RFIC does not have knowledge of the supplied data rate, and thus cannot determine the appropriate Gaussian lowpass filter function to apply to the incoming data.

One advantage of this mode that it saves a microcontroller pin because no TX Clock output function is required. The primary disadvantage of this mode is the increase in occupied spectral bandwidth with FSK (as compared to GFSK).

#### 4.2.2.3. Direct Mode using SPI or nIRQ Pins

In certain applications it may be desirable to minimize the connections to the microcontroller or to preserve the GPIOs for other uses. For these cases it is possible to use the SPI pins and nIRQ as the modulation clock and data. The SDO pin can be configured to be the data clock by programming trclk = 10. If the nSEL pin is LOW then the function of the pin will be SPI data output. If the pin is high and trclk[1:0] is 10 then during TX mode the data clock will be available on the SDO pin. If trclk[1:0] is set to 11 and no interrupts are enabled in registers 05 or 06h, then the nIRQ pin can also be used as the TX data clock.

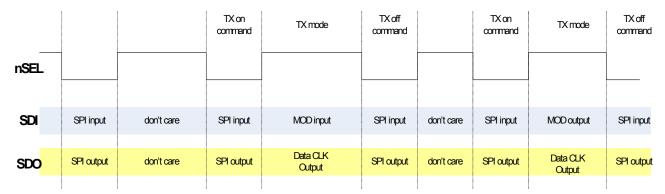

The SDI pin can be configured to be the data source in TX mode if dtmod[1:0] = 01. In a similar fashion, if nSEL is LOW the pin will function as SPI data-in. If nSEL is HIGH then in TX mode it will be the data to be modulated and transmitted. Figure 9 demonstrates using SDI and SDO as the TX data and clock:

**Figure 9. Microcontroller Connections**

If the SDO pin is not used for data clock then it may be programmed to be the interrupt function (nIRQ) by programming Reg 0Eh bit 3.

#### 4.2.3. PN9 Mode

In this mode the TX Data is generated internally using a pseudorandom (PN9 sequence) bit generator. The primary purpose of this mode is for use as a test mode to observe the modulated spectrum without having to provide data.

## 5. Internal Functional Blocks

This section provides an overview some of the key blocks of the internal radio architecture.

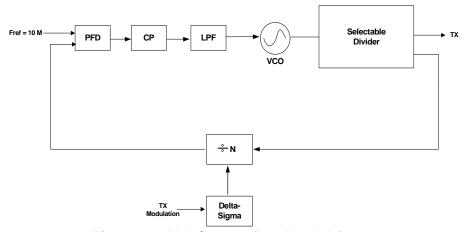

## 5.1. Synthesizer

An integrated Sigma Delta ( $\Sigma\Delta$ ) Fractional-N PLL synthesizer capable of operating from 240–960 MHz is provided on-chip. The Si4031/32 and Si4030 cover different frequencies. This section discusses the frequency range covered by all EZRadioPRO devices. Using a  $\Sigma\Delta$  synthesizer has many advantages; it provides flexibility in choosing data rate, deviation, channel frequency, and channel spacing. The transmit modulation is applied directly to the loop in the digital domain through the fractional divider which results in very precise accuracy and control over the transmit deviation.

Depending on the part, the PLL and  $\Delta$ - $\Sigma$  modulator scheme is designed to support any desired frequency and channel spacing in the range from 240–960 MHz with a frequency resolution of 156.25 Hz (Low band) or 312.5 Hz (High band). The transmit data rate can be programmed between 0.123–256 kbps, and the frequency deviation can be programmed between  $\pm 1$ –320 kHz. These parameters may be adjusted via registers as shown in "3.5. Frequency Control" on page 22.

Figure 10. PLL Synthesizer Block Diagram

The reference frequency to the PLL is 10 MHz. The PLL utilizes a differential L-C VCO, with integrated on-chip inductors. The output of the VCO is followed by a configurable divider which will divide down the signal to the desired output frequency band. The modulus of this divider stage is controlled dynamically by the output from the  $\Delta$ - $\Sigma$  modulator. The tuning resolution is sufficient to tune to the commanded frequency with a maximum accuracy of 312.5 Hz anywhere in the range between 240–960 MHz.

#### 5.1.1. VCO

The output of the VCO is automatically divided down to the correct output frequency depending on the hbsel and fb[4:0] fields in "Register 75h. Frequency Band Select." The VCO integrates the resonator inductor, tuning varactor, so no external VCO components are required.

The VCO uses a capacitance bank to cover the wide frequency range specified. The capacitance bank will automatically be calibrated every time the synthesizer is enabled. In certain fast hopping applications this might not be desirable so the VCO calibration may be skipped by setting the appropriate register.

## 5.2. Power Amplifier

The Si4032 contains an internal integrated power amplifier (PA) capable of transmitting at output levels between –1 and +20 dBm. The Si4030/31 contains a PA which is capable of transmitting output levels between –8 to +13 dBm. The PA design is single-ended and is implemented as a two stage class CE amplifier with a high efficiency when transmitting at maximum power. The PA efficiency can only be optimized at one power level. Changing the output power by adjusting txpow[2:0] will scale both the output power and current but the efficiency will not be constant. The PA output is ramped up and down to prevent unwanted spectral splatter.

## 5.2.1. Output Power Selection

With the Si4032, the output power is configurable in 3 dB steps with the txpow[2:0] field in "Register 6Dh. TX Power." Extra output power can allow the use of a cheaper, smaller antenna reducing the overall BOM cost. The higher power setting of the chip achieves maximum possible range, but of course comes at the cost of higher TX current consumption. However, depending on the duty cycle of the system, the effect on battery life may be insignificant. Contact Silicon Labs Support for help in evaluating this tradeoff.

The +13 dBm output power of the Si4030/31 is targeted at systems that require lower output power. The PA still offers high efficiency and a range of output power from –8 to +13 dBm.

| Add | R/W | Function/Description | D7 | D6 | D5 | D4 | D3 | D2       | D1       | D0       | POR Def. |

|-----|-----|----------------------|----|----|----|----|----|----------|----------|----------|----------|

| 6D  | R/W | TX Power             |    |    |    |    |    | txpow[2] | txpow[1] | txpow[0] | 07h      |

| txpow[2:0] | Si4032 Output Power |

|------------|---------------------|

| 000        | +1 dBm              |

| 001        | +2 dBm              |

| 010        | +5 dBm              |

| 011        | +8 dBm              |

| 100        | +11 dBm             |

| 101        | +14 dBm             |

| 110        | +17 dBm             |

| 111        | +20 dBm             |

| txpow[2:0] | Si4030/31 Output Power |

|------------|------------------------|

| 000        | –8 dBm                 |

| 001        | –5 dBm                 |

| 010        | –2 dBm                 |

| 011        | +1 dBm                 |

| 100        | +4 dBm                 |

| 101        | +7 dBm                 |

| 110        | +10 dBm                |

| 111        | +13 dBm                |

## 5.3. Crystal Oscillator